Porta

logica AND

La

versione di valutazione del programma Design Lab della MicroSim contiene nella

libreria EVAL, oltre a vari componenti elettronici, anche circuiti digitali

della famiglia logica TTL standard.

In questa prima esercitazione ci proponiamo

di verificare la tabella della verità della porta logica AND contenuta nel chip

7408 con due metodi differenti:

- applicando in ingresso,

di volta in volta, le possibili combinazioni e verificando in uscita il

livello logico ottenuto.

- applicando in ingresso

due generatori di onde quadre: il primo, con tempi TH=TL=0.5us, al pin 1 ed

il secondo, con tempi TH=TL=1us, al pin 2.

Metodo

1

Dopo

aver eseguito il programma Schematic Editor si porta sul foglio di lavoro la

porta logica AND contenuta nel chip 7408.

Per

far ciò si attiva il comando Draw/Get New Part/7408 (oppure il comando

rapido CTRL+G/7408). Si noti che la finestra di dialogo ottenuta, ci mostra, in

anteprima, la sagoma del componente. Fare click su Place & Close per

inserire il componente desiderato sul foglio di lavoro. Spostarsi col mouse per

portare la porta logica nella posizione voluta e poi fare click di sinistro per

piazzarlo definitivamente e poi click di destro per uscire dalla modalità di

inserimento di quel componente.

Applichiamo i livelli logici in ingresso.

MicroSim presenta due sorgenti di segnali digitali che si chiamano LO (low =

livello logico basso, 0) e HI (high = livello logico alto, 1). Essi si prelevano

dalla libreria col solito comando Draw/Get New Part.

Inseriamo sul terminale di uscita della porta

AND, infine, il connettore Global dalla libreria Port col comando Get/New

Part/Global. Il connettore presenta, alla destra del simbolo, il terminale

da collegare alla porta logica. Il connettore, perciò, deve essere ruotato di

180°. Per ottenere ciò è sufficiente eseguire il comando Edit/Rotate

(oppure CTRL+R) per due volte. Infatti, il comando “rotate” determina

una rotazione di 90° in senso antiorario. Bisogna assicurarsi di aver

selezionato il componente da ruotare. Per selezionare un componente è

sufficiente fare click una sola volta sullo stesso componente.

Assegniamo al connettore Global il nome Y. Si

faccia doppio click nella sagoma del connettore. Si ottiene una finestra di

dialogo nella quale inseriamo il nome: Y seguito da click sul pulsante OK.

Forniamo, infine, un titolo, al nostro

circuito. Draw/Text e nella finestra di dialogo ottenuta scriviamo

“Porta logica AND”.

|

|

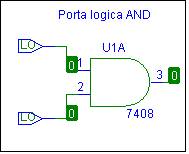

Fig.1

- Schema logico costituito dalla porta AND contenuta nel circuito

integrato 7408 della famiglia logica TTL standard.

Si

evidenziano i due ingressi LO, il connettore Global in uscita ed il

testo inserito per specificare il titolo.

|

Salvare il file realizzato col comando File/Save.

Inserire il nome AND.SCH.

Per eseguire la simulazione di

funzionamento fare click, preliminarmente, sul pulsante V della barra degli

strumenti e poi eseguire il comando Analysis/Simulate (o F11).

Sulle linee di ingresso ed uscita

appariranno i valori logici corrispondenti.

Per ripetere la simulazione di funzionamento

per le altre combinazioni di ingresso è sufficiente cancellare l’ingresso LO

col comando Edit/Delete e

sostituirlo con l’ingresso HI e poi ripetere il comando di avvio simulazione

con Analysis/Simulate (o F11).

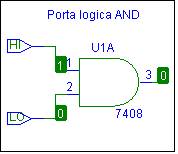

Fig.2

– Simulazioni per tre delle quattro possibili combinazioni di ingresso.

Proposta di lavoro:

Sostituire al 7408 le seguenti

porte logiche: 7400 NAND, 7402 NOR, 7432 OR, 7486 XOR verificando le relative

tabelle della verità.

Metodo 2

-

Inserire due generatori di

onde quadre agli ingressi: Get/New Part/DigClock.

-

Fare doppio click nella

sagoma del primo generatore ed impostare i seguenti valori:

DELAY=0 Save attribute.

-

Lasciamo, perché buoni, i

valori ONTIME=0.5us (0,5micro secondi), OFFTIME=0.5us e STARTVAL=0.

-

Click su OK.

-

Per il secondo generatore

impostiamo, invece, DELAY=0, ONTIME=1us, OFFTIME=1us e STARTVAL=0.

|

|

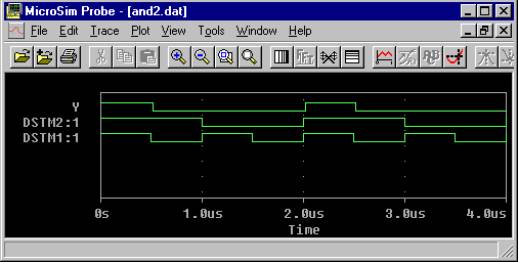

Fig.3

– Porta AND pilotata da due generatori di onde quadre con periodo 1us e

2 us.

Analizzando

le onde quadre, istante per istante, si osservano le quattro combinazioni

possibili tra gli ingressi.

Per

ottenere la visualizzazione di ONTIME e OFFTIME fare doppio click

all’interno della sagoma del generatore, fare click sulla voce ONTIME e

poi sul pulsante Change Display e selezionare la voce “both name and

value”.

|

Poiché si desidera la visualizzazione della

simulazione in funzione del tempo si deve prima eseguire il “Setup” col

comando Analysis/Setup. Fare click sulla casella Transient (in funzione

del tempo) e click sul relativo pulsante. Impostare i seguenti tempi: FINAL TIME

= 4000ns (cioè 4 microsecondi) in modo da visualizzare due periodi completi del

generatore DSTM2.

Per avviare la simulazione si attiva il

comando Analysis/Simulate. Si dovrebbero ottenere le forme d’onda mostrate

nella seguente figura 4.

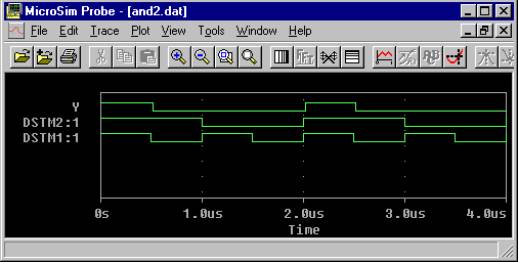

Fig.4 – Forme d’onda

del circuito di fig.3. Si osservi che l’uscita Y assume il valore alto ( 1 )

solo quando entrambi gli ingressi DSTM1 e DSTM2 sono al livello alto. In tutti

gli altri casi l’uscita vale 0.

Per analizzare meglio i valori digitali delle

forme d’onda ottenute si attivi il comando Tools/Cursor/Display del

programma Probe.

Facendo

click col mouse e trascinando a destra e sinistra si osserverà il marker

verticale che si muove corrispondentemente mentre sul lato sinistro del display,

accanto ai nomi delle forme d’onda, appaiono i valori numerici 0 o 1 delle

singole forme d’onda.

Facendo click sul pulsante destro del mouse

è possibile manovrare un secondo cursore diverso da quello attivato col

pulsante sinistro del mouse.

Proposta

di lavoro:

Anche

in questo caso si provi a sostituire al 7408 altre porte logiche a due entrate

per verificarne la tabella della verità.

Si

provi, inoltre a variare i tempi ONTIME, OFFTIME dei generatori per osservare,

poi, le forme d’onda così modificate.